- 全部

- 默认排序

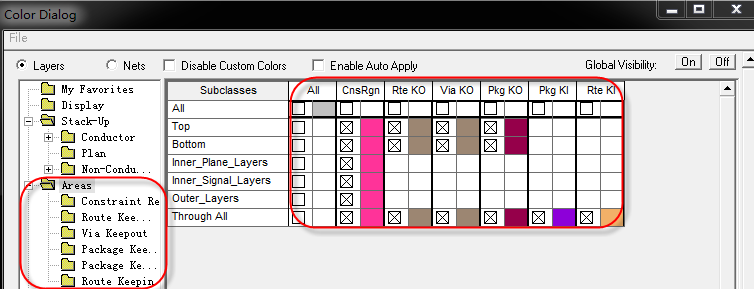

答:我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。

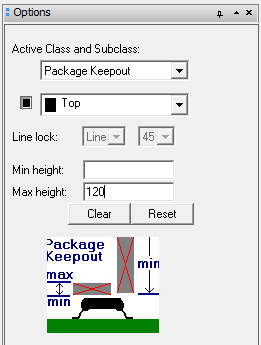

答:我们在进行一些复杂的PCB设计时,都会有很多结构限制,比如这里限高3MM等需求,为了辅助工程师们更好的进行设计,我们需要在PCB区域内绘制限高区域,并设置限高的参数,具体操作如下所示:第一步,在PCB板上绘制需要限高的区域,执行菜单命令Setup-Areas,在下拉菜单中选择Package Keepout,如图5-66所示,显示器件禁布区。

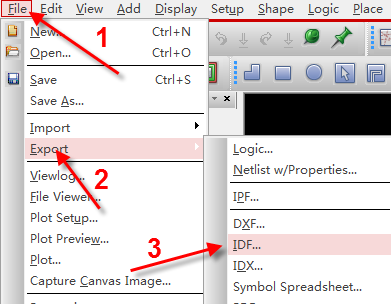

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

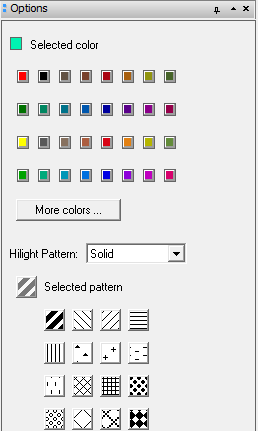

答:高亮显示命令,也就是Assign Color命令。在Allegro软件进行PCB设计的时候,是应用非常广泛的命令,如图5-76所示。这里我我们详细介绍一下,高亮显示的使用方法以及在Options参数面板的设置,具体如下:

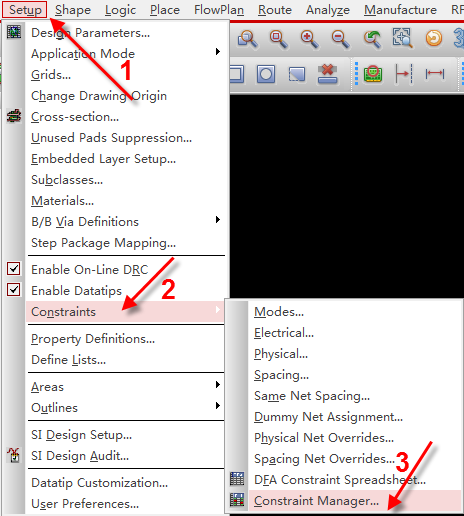

答:我们在设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

答:在PCB设计过程中,对于大电流的电路或者是网络,我们都会采用铺铜的方式去解决。在Allegro软件中,铺铜的命令有好多个,如图5-126所示,为了更方便的学习好铜皮处理的各个命令,这里我们讲述一下铜皮处理的相关命令具体含义:

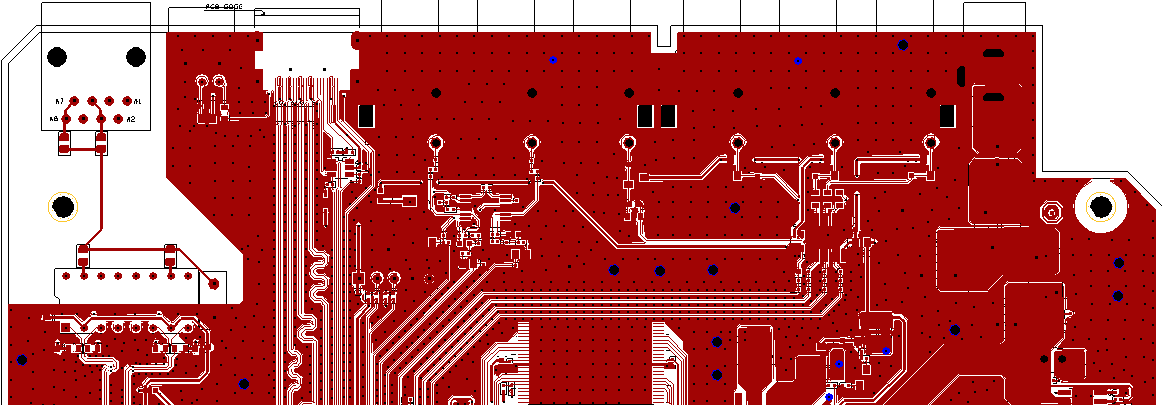

答:我们在使用Allegro软件进行PCB设计时,铺的铜皮都是动态或者是静态的铜皮,当打开Etch的时候,所有的走线跟铜皮都是同时显示的,如图5-130所示,在Allegro软件中是否可以隐藏铜皮呢,只显示走线呢,答案是可以的,具体操作如下:

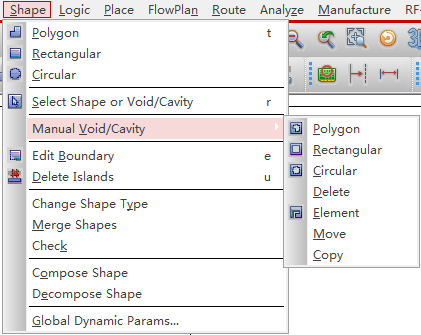

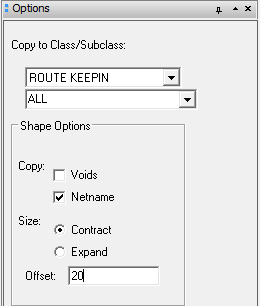

答:我们在PCB设计过程中,复制是经常使用的命令,而copy命令,如图5-134所示,一般只能复制对象到相同的class/subclass,对于不同class/subclass之间的拷贝呢,使用的命令是Zcopy命令,如图5-135所示。具体使用的步骤如下所示:

答:走线命令或者是叫做拉线命令,是PCB设计中一个非常重要的命令,我们这里对走线命令的一些详细的设置介绍一下。执行菜单命令Route-Connect,就是走线命令,如图5-140所示,然后在Find面板中,默认的选项是勾上的,勾上这些选项以后呢,走线的时候,才可以连接上行,比如勾上pins,这样走线的时候,才可以连接到焊盘,不然是连接不上的,如图5-141所示。

扫码关注

扫码关注